# AN IMPROVEMENT OF ULTRA LOW POWER, VOLTAGE AND TEMPERATURE INSENSITIVE CMOS VOLTAGE REFERENCE

WORAWAT SA-NGIAMVIBOOL<sup>1</sup>, WACHIRAPUNYA PUNYAWONG<sup>2</sup>

Key words: CMOS, Voltage reference, Subthreshold, Temperature compensation, Low voltage, Low power.

This paper presents the design of a CMOS voltage reference circuit. In the past, the design of a CMOS voltage reference circuit consisted of a lot of active and passive devices or required an external startup circuit. Therefore, this research presents the design of a voltage reference circuit using all CMOS without parasitic bipolar junction transistors (BJT) and passive devices, which cause loss of power and consume a large chip area. It can be operated without external startup circuit. The result of PSPICE (personal simulation program with IC emphasis) simulation program has been verified that the circuit can operate with stability. The supply voltage is only 1.8 V, reference voltage levels of about  $259 \pm 2.5$  mV, the standard temperature coefficient of 95.15 ppm/°C, ranges from -20 to 100 °C and a low power dissipation of 2.93  $\mu$ W.

#### 1. INTRODUCTION

Voltage reference circuits have been developed continuously. In particular, CMOS voltage reference circuit presented in the past research is widely used in electronic circuits application such as analog-to-digital and digital-to-analog conversion circuit, oscillators, memory and many more of them [1, 2]. In addition, it can be used with many types of devices such as daily-used portable devices which can be smaller in size with lower consumption [3, 6]. In the past, CMOS voltage reference circuit was developed in many ways such as reducing it to a lower voltage operation [5, 7] and chip area [2, 4] or using the parasitic BJT [8, 12]. These circuits still have some areas to create diode for generating negative and positive current for the temperature coefficient [13].

Therefore, this paper presents all CMOS voltage reference circuit design based on subthreshold voltage without parasitic BJT and external startup circuit by new current summation technique that has opposite coefficient for reference voltage generation which stabilize supply voltage and temperature variations.

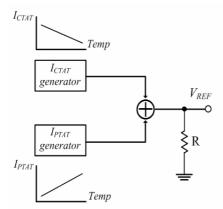

#### 2. PRINCIPLE OF A VOLTAGE REFERENCE

The first part is the current generator circuit with a positive temperature coefficient or proportional to absolute temperature (PTAT). Second part is used for generating the current that has negative temperature coefficient or complementary to absolute temperature (CTAT). Both currents are summed together. The stable voltage ( $V_{REF}$ ) with a temperature coefficient (TC) can be achieved by this methodology.

## 3. THE PROPOSED CMOS VOLTAGE REFERENCE

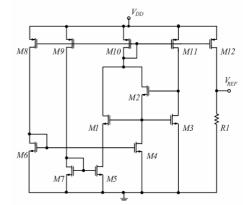

The proposed CMOS voltage reference circuit is shown in Fig. 2.

Fig. 2 - Proposed CMOS voltage reference circuit.

The MOS transistors M1 and M3 operated in the subthreshold region is defined as the operating region of the MOS transistor at very low drain currents, with the gate-source voltage  $V_{GS}$  values around the threshold voltage  $V_{th}$  as adopted by [4]:

$$V_{GS} < V_{th} \,. \tag{1}$$

Fig. 1 - Proposed CMOS voltage reference circuit.

The  $V_{GS}$  of M1 and M3 can be calculated using the current equation in subthreshold regions, as stated below [7]:

The principle of the presented circuit consists of three parts as shown in Fig. 1.

<sup>1</sup> Mahasarakham University, Faculty of Engineering, Khantarawichai, Mahasarakham, 44150 Thailand, E-mail: wor\_nui@yahoo.com

<sup>&</sup>lt;sup>2</sup> Khonkaen Technical College, Division of Computer Technology, Khonkaen, 40000 Thailand, E-mail: wpw58mail@gmail.com (Corresponding author)

$$V_{GS_{M1}} = nV_T \ln\left(\frac{I_{ds1} \cdot L_1}{I_t \cdot W_1}\right) + V_{th}$$

(2)

$$V_{GS_{M3}} = nV_T \ln\left(\frac{I_{ds3} \cdot L_3}{I_t \cdot W_3}\right) + V_{th}$$

(3)

where

$$V_T = \frac{kT}{q},\tag{4}$$

and  $V_T$  – is thermal voltage; k – is Boltzmann constant, equal to  $1.38 \times 10^{-23}$  J/°K; q – is electric charges, equal to  $1.6 \times 10^{-19}$  C; T – is test temperature (°K); n – is slope factor in PSPICE, determined to be between 1.5 to 2;  $I_t$  – is saturation current of MOS transistor.

The MOS transistors M2, M4, M6 and M7 are defined to operate in the saturation region. The I-V characteristic of a MOS transistor in the saturation region can be well approximated as [5]:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2, \qquad (5)$$

where *W* and *L* is channel width and channel length of the transistor,  $C_{ox}$  is the value of capacitance per unit area of the gate oxide (electron charge per unit area),  $V_{th}$  is the threshold voltage and  $\mu_n$  is the carrier mobility, respectively.

For MOS transistor, the primary parameters that are affected by temperature in equation (5) are the threshold voltage  $V_{th}$  and the carrier mobility  $\mu_n$ . The mobility  $\mu_n$  depends on the [9]:

$$\mu_n(T) = \mu_n(T_0) \left(\frac{T}{T_0}\right)^{-\beta_\mu}, \qquad (6)$$

where  $\mu_n(T_0)$  is the mobility of electrons at room temperature,  $T_0$  is room temperature (300° K), T is the test temperature and  $\beta_{\mu}$  is the mobility temperature exponent. The following equation (6) demonstrates the value change of  $\mu_n(T)$  at test temperature. That is, when the temperature increases, then  $\mu_n(T_0)$  will decrease.

The dependence of the threshold voltage  $V_{th}$  to temperature variation is expressed as:

$$V_{th} = V_{th}(T_0) + \alpha_{V_{th}} (T - T_0), \qquad (7)$$

where  $T_0$  is the reference temperature,  $\alpha_{Vth}$  is normally a negative constant. From (7),  $V_{th}$  decreases with elevation of the temperature.

The first part is composed of M1, M3, M5 and M7. The  $V_{GS}$  in M3 is equal to the sum of  $V_{GS}$  in M1 and drain-source voltage  $V_{DS}$  in M5 can be written as:

$$V_{GS_{M3}} = V_{GS_{M1}} + V_{DS_{M5}}$$

(8)

From equation (8) we get:

$$V_{DS_{M5}} = V_{GS_{M3}} - V_{GS_{M1}}.$$

(9)

Then, the voltage  $V_{DS}$  of M5 can be express as:

$$V_{DS_{M5}} = nV_T \ln \left( \frac{I_{ds_{M3}} \cdot W_1 / L_1}{I_{ds_{M1}} \cdot W_3 / L_3} \right).$$

(10)

The M5 operating in a linear region uses a modified beta-multiplier self-bias circuit using a MOS resistor, M5, instead of ordinary resistor, as shown in the following equation [9]:

$$R_{\rm M5} = \frac{1}{\mu_n c_{ox} \frac{W_5}{L_5} \left( V_{GS_{\rm M5}} - V_{th} \right)}.$$

(11)

Using equations (10) and (11), we can express  $I_{\text{PTAT}}$  as:

$$I_{D_{\rm M5}} = I_{\rm PTAT} = \frac{V_{DS_{\rm M5}}}{R_{\rm M5}}, \qquad (12)$$

yielding

$$I_{\rm PTAT} = \frac{nV_T}{R_{\rm M5}} \ln \left( \frac{I_{ds_{\rm M3}} \cdot W_1 / L_1}{I_{ds_{\rm M1}} \cdot W_3 / L_3} \right).$$

(13)

The study reveals in equation (13), that the current  $I_{D_{M5}}$  has a positive temperature coefficient; it's clearly seen that when temperature increases in  $V_T$ , the current  $I_{D_{M5}}$  will increase.

The second part is composed of M3, M4 and M6. The M3 is defined to operate in the subthreshold region and the  $V_{GS}$  of M3 is in equation (3). The gate-source voltage in M6 provides a gate-source voltage for M4 and they are both defined to operate in a saturation region. The following relations find that:

$$V_{GS_{M6}} = V_{GS_{M4}} . \tag{14}$$

The equation for drain current  $(I_D)$  of M4 is given by:

$$I_{D_{M4}} = \frac{1}{2} \mu_n C_{ox} \frac{W_4}{L_4} (V_{GS_{M4}} - V_{th})^2 .$$

(15)

Hence, the drain current has a square-law dependence on the gate-source voltage and the transconductance of M4 is found from differentiating equation (15) with respect to  $V_{GS}$  obtained [13]:

$$g_{M4} = \frac{\partial I_{D_{M4}}}{\partial V_{GS_{M4}}} = \frac{1}{2} \mu_n C_{ox} \frac{W_4}{L_4} 2 \left( V_{GS_{M4}} - V_{th} \right)$$

(16)

and we can obtain:

$$g_{_{M4}} = \mu_n C_{ox} \frac{W_4}{L_4} \left( V_{GS_{M4}} - V_{th} \right), \tag{17}$$

since

$$R_{\rm M4} = \frac{1}{g_{\rm M4}} = \frac{1}{\mu_n C_{ox} \frac{W_4}{L_4} (V_{GS_{\rm M4}} - V_{th})}.$$

(18)

Using equations (3) and (18), we arrive at the expression:

$$I_{D_{\rm M4}} = \frac{V_{GS_{\rm M3}}}{R_{\rm M_4}},$$

(19)

yielding

$$I_{D_{M4}} = \frac{nV_T}{R_{M4}} \ln \left( \frac{I_{d_{S_{M3}}}}{I_t} \cdot \frac{L_3}{W_3} \right) + V_{th}.$$

(20)

It reveals in equation (20) that  $I_{D_{M4}}$  will decrease as temperature increases which is called  $I_{CTAT}$ . As shows in equation (19), this implies that the  $V_{GS_{M3}}$  is quite small and decreases with the temperature increases [4, 10].

In the last part, the mirror circuit consists of MOS transistor M8 to M12. A reference current ( $I_{REF}$ ) is the sum of  $I_{PTAT}$  and  $I_{CTAT}$  by the MOS transistor M10. This can be expressed as:

$$I_{REF} = I_{\text{PTAT}} + I_{\text{CTAT}}.$$

(21)

By using equation (13) and (20), we can express the reference current as:

$$I_{REF} = \frac{nV_T}{R_{M5}} \ln \left( \frac{I_{ds_{M3}}}{I_{ds_{M1}}} \cdot \frac{K_1}{K_3} \right) + \frac{nV_T}{R_{M4}} \ln \left( \frac{I_{ds_{M3}}}{I_t} \cdot \frac{1}{K_3} \right) + V_{th} , \qquad (22)$$

where  $K_1 = W_1/L_1$  and  $K_3 = W_3/L_3$ .

The  $I_{REF}$  is sourced on a resistor R1, thus the reference voltage can be obtained as follows:

$$V_{REF} = I_{REF} R 1.$$

(23)

The output reference voltage can be adjusted to any level by changing the resistance value of R1 and the reference voltage remains stable when the following condition is satisfied [4, 11]:

$$\frac{\partial V_{REF}}{\partial T} = 0 .$$

(24)

The voltage reference with a TC formed by the min/max limits for the nominal output voltage over the operating temperature range is defined as follows:

$$TC = \frac{1}{V_{atroomtemp}} \left[ \frac{V_{max} - V_{min}}{T_{min} - T_{min}} \right] \cdot 10^{6} \left[ ppm/^{\circ}C \right]$$

(25)

The voltage reference circuit exhibits a TC limit typically between 20 to 100 ppm/°C [12].

# 4. SIMULATION RESULTS

The TSMC 0.35  $\mu$ m of CMOS technology was used to evaluate the performance of the proposed circuit, verified by PSPICE software and a supply voltage  $V_{DD} = 1.8$  V. Table 1 shows the parameter size of MOS transistors and resistor.

#### Table 1

The parameters of transistors and resistors

| Transistors        | $W/L(\mu m/\mu m)$ |

|--------------------|--------------------|

| M1                 | 6 / 2.9            |

| M2                 | 6 / 5              |

| M3                 | 8 / 2.3            |

| M4                 | 1.3 / 2.4          |

| M5                 | 2 / 2.4            |

| M6                 | 4.1 / 3.4          |

| M7                 | 2.2 / 1.9          |

| M8 - M11           | 5 / 5              |

| M12                | 8 / 5              |

| Aspect ratio M1/M3 | 2                  |

| Resistors          | (kΩ)               |

| <i>R</i> 1         | 550                |

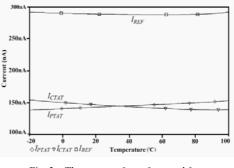

Figure 3 shows the direction when  $I_{\text{PTAT}}$  and  $I_{\text{CTAT}}$  were changed, which is associated with the temperature range of -20 to 100 °C.

Fig. 3 – The currents  $I_{\text{CTAT}}$ ,  $I_{\text{PTAT}}$  and  $I_{REF}$  as a function of the temperature.

$I_{\text{CTAT}}$  will decrease as the temperature increases and  $I_{\text{PTAT}}$  is increased as the temperature increases. Then the two are combined at MOS transistor M10 to create the current  $I_{REF}$ , which is constant and has a low impact on the change in temperature.

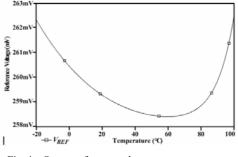

Figure 4 shows the output reference voltage as a function at room temperature, that indicates about 259 mV, the voltage variation less than 2.5 mV, the temperature variations of  $-20^{\circ}$ C to  $100^{\circ}$ C, and the temperature coefficient is 95.15 ppm/°C.

Fig. 4 - Output reference voltage versus temperature.

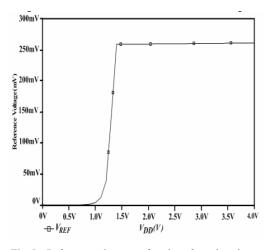

Simulation result shows that the proposed voltage reference generates a mean reference voltage of about 259

mV with a variation of 1.0 mV/V at room temperature and the power consumption is 2.93  $\mu$ W, when the supply voltage increases from 1.8 V to 4.0 V, as shown in Fig. 5.

Fig. 5 - Reference voltage as a function of supply voltage.

# 5. CONCLUSIONS

An all CMOS voltage reference circuit presented in this paper, can work without the external startup circuit, and the work is not complicated because it generates and sums positive and negative currents to a stable voltage reference. This reduces the number of devices that are used as the main components of the circuit. As a result, the circuit consumes lower power. It can be further developed as an integrated circuit. In this circuit, the temperature range is wide (-20 to 100 °C), and stable to supply voltage variation (1.0 mV/V), with a low temperature coefficient of 95.15 ppm/°C, in the TSMC 0.35  $\mu$ m CMOS technology, and the output voltage can be adjusted by the output resistor.

# ACKNOWLEDGEMENTS

The authors would like to thank all reviewers for their helpful comments which greatly help improve this work and we also thank the Department of Electrical and Computer Engineering, Faculty of Engineering, Mahasarakham University, Mahasarakham, Thailand.

Received on December 12, 2015

# REFERENCES

- Henri J. Oguey, Daniel Aebisher, CMOS current reference without resistance, IEEE J. Solid-State Circuits., 32, 7, pp. 1132–1135 (1997).

- A. Boni, Op-Amps and startup circuits for CMOS bandgap references with near 1-V supply, IEEE J. Solid-State Circuits., 37, 3, pp. 1339–1343 (2002).

- Giuseppe De Vita, Giuseppe Iannaccone, A sub-1, 10 ppm/°C nanopower voltage reference generator, IEEE J. Solid-State Circuits., 42, 7, pp. 1536–1542 (2006).

- Po-Hsuan Huang, Hongchin Lin, Yen-Tai Lin, A simple subthreshold CMOS voltage reference circuit wit channellength modulation compensation, IEEE Tran., Circuits Systems II., 53, 9, pp. 882–885 (2006).

- G. Giustolisi, P. Gaetano, C. Marcello, C. Fulvio, A low-voltage low-power voltage reference based on subthreshold MOSFETs, IEEE J. Solid-State Circuits., 38, 1, pp. 151–154 (2003).

- Radu H. Iacob, Anca Manolescu, Current-mode references based on mos subthresold operation, U.P.B. Sci. Bull., 71, pp. 15–28 (2009).

- Wachirapunya Punyawong, Warawat Sa-Ngiamvibool, Apinun Aurasopon, Sweth Hongprasit, *An improvement of CMOS voltage reference*, Przegląd Elektrotechniczny (Electrical Review), **89**, 6, pp. 109–111 (2013).

- L. Yongjia, X. Xiaojuan, S. Weifeng, L. Shengli, A 760mV voltage reference with mobility and Subthreshold slope compensation, IEEE International Conference, 8, pp. 1145–1148 (2009).

- Ken Ueno, T. Hirose, T. Asai, A 300nW, 15 ppm/°C, 200 ppm/V CMOS voltage reference circuit, IEEE J. Solid-State Circuits., 44, 7, pp. 2047–2054 (2009).

- Cosmin Popa, CMOS Logarithmic Curvature-Corrected voltage references by using a multiple differential structure, Rev. Roum. Sci. Techn. – Électrotechn. et Énerg., 55, 4, pp. 436–444 (2010).

- Luca Magnelli, Felice Crupi, Paquale Corsonello, A 2.6 nW, 0.45 V temperature-compensated subthreshold CMOS voltage reference, IEEE J. Solid-State Circuits., 46, 2, pp. 465–474 (2011).

- Rajarshi Paul, Amit Patra, *Trimming process and temperature* variation in second-order bandgap voltagte reference circuits, Microelectronics Journal., 43, pp. 89–97 (2011).

- Michał Łukaszewicz, Tomasz Borejko, Witold A. Pleskacz, A 65 nm CMOS resistorless current reference source with low sensitivity to PVT variations, International Journal of Microelectronics and Computer Science, 3, 4, pp. 119–124 (2012).

- Abhishek Pandey, Divya Yadav, Ritika Singh, Vijay Nath, Design of Ultra Low Power CMOS Temperature Sensor for Space Application, IJAREEIE., 2, 8, pp. 4117–4125 (2013).

- 15. Ze-kun Zhou, Yue Shi, Xi Qu, Hui-ying Wang, Xiao-min Zhang, Shi Qiu, Nie Li, Chao Gou, Zhuo Wang, Bo Zhang, A CMOS Voltage Reference Based on Mutual Compensation of Vtn and Vtp, IEEE Trans, Circuits Systems II, 59, 6, pp. 341–345 (2012).

- Yanhan Zeng, Yunling Luo, Jun Zhan, Zhugian Gong, Hong-Zhou Tan, A low power CMOS voltage reference based on body effect, IEICE Electronics Express, 10, 8, pp. 1–6 (2013).

- Byung-Do Yang, 250-mV Supply Subthreshold CMOS Voltage Reference Using a Low-Voltage Comparator and a Charge-Pump Circuit, IEEE Trans Circuits and Systems, 61, 11, pp. 850–854 (2014).

- Shailesh S. Chouhan, Kari Halonen, Design and Implementation of all MOS micro-power Voltage Reference Circuit, Analog Integrated Circuit Signal Process, 80, pp. 399–406 (2014).

- Shailesh S. Chouhan, Kari Halonen, Design and Implementation of a micro power CMOS voltage reference circuit based on thermal compensation of Vgs, Microelectronics, 46, pp. 36–42 (2015).